在当代集成电路设计的宏大版图中,金属氧化物半导体场效应晶体管(MOSFET)无疑是构筑所有数字与模拟系统的基石。无论是智能手机中高速运算的处理器,还是电动汽车里高效的能量管理芯片,其内部都密布着数以亿计的MOSFET。理解MOSFET的工作原理、特性及其在电路设计中的应用,是每一位集成电路工程师的必修课。

一、MOSFET:从物理结构到电气特性

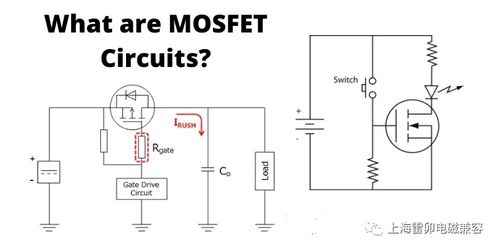

MOSFET是一种通过电场效应控制电流通断的三端器件(源极、漏极、栅极)。其核心在于栅极下的沟道形成与夹断。根据沟道类型,主要分为N沟道(NMOS)和P沟道(PMOS)。当栅极电压超过阈值电压时,导电沟道形成,器件开启。这种电压控制电流的特性,使其成为理想的开关和放大元件。

关键的电气特性包括:

- 转移特性:描述了漏极电流与栅源电压的关系,决定了开关的阈值和跨导。

- 输出特性:展示了漏极电流与漏源电压在不同栅压下的关系,区分了线性区、饱和区和截止区。

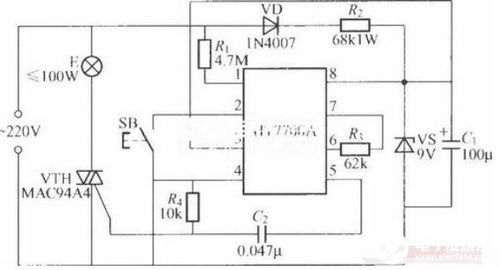

- 寄生参数:如栅源/栅漏电容、源漏电阻等,这些参数直接决定了电路的开关速度、功耗和频率响应,是高频与高速电路设计中的关键考量。

二、CMOS技术:现代数字电路的支柱

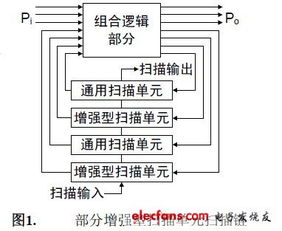

互补金属氧化物半导体(CMOS)技术将NMOS和PMOS晶体管成对使用,构成了当今几乎所有数字集成电路的基础。一个基本的CMOS反相器由一个上拉的PMOS和一个下拉的NMOS组成。其最大优点在于静态功耗极低:在稳定逻辑状态下,总有一条通路被完全切断,只有极微小的漏电流。这种低功耗特性使得高密度、超大规模集成成为可能。从逻辑门(与非、或非门)到触发器,再到复杂的处理器内核,都是由这些基本的CMOS单元组合、级联而成。

三、模拟电路设计中的MOSFET艺术

在模拟集成电路中,MOSFET的角色从单纯的开关演变为精密的信号处理元件。

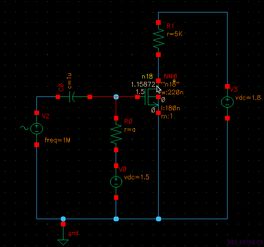

- 放大电路:共源极、共栅极、共漏极(源极跟随器)是三种基本组态,用于实现电压放大、电流缓冲和阻抗变换。设计需精心偏置晶体管进入饱和区,并权衡增益、带宽、线性度和噪声性能。

- 电流镜与偏置电路:利用两个或多个具有相同栅源电压的MOSFET,可以精确复制电流,为整个芯片提供稳定可靠的偏置参考,是模拟IC的“心脏”。

- 开关与模拟开关:利用其近乎理想的开关特性(高关断电阻、低导通电阻),用于采样保持电路、数据转换器和可编程增益放大器等。

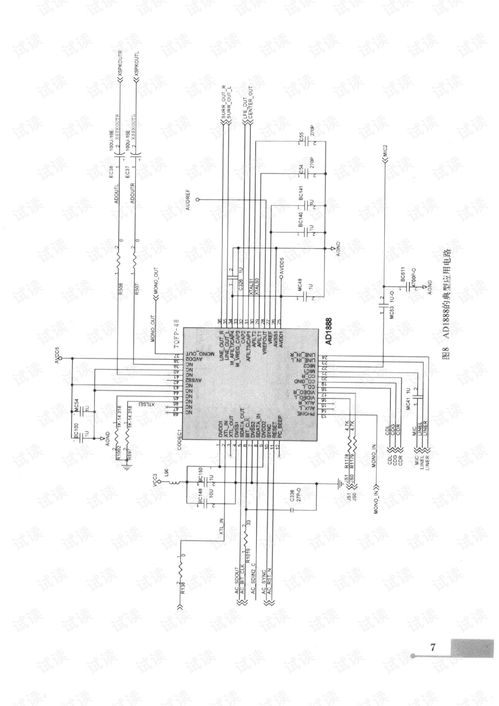

- 射频与混合信号设计:在GHz频率下,MOSFET的寄生电容、电感效应变得至关重要。设计需要深入考虑噪声系数、线性度(IP3)、匹配网络和衬底耦合等复杂问题。

四、先进工艺下的挑战与设计考量

随着工艺节点进入纳米尺度(如7nm、5nm乃至更小),MOSFET的设计面临着前所未有的挑战:

- 短沟道效应:沟道长度缩短导致阈值电压漂移、漏致势垒降低等,使器件的控制变得困难。

- 功耗墙:动态功耗与CV²f成正比,而静态功耗因亚阈值漏电流加剧而显著上升。低功耗设计(如多阈值电压、电源门控、近阈值计算)成为核心。

- 工艺变异:纳米尺度下,原子级别的工艺波动会导致器件参数(如阈值电压、沟道长度)出现显著随机偏差,设计必须具有足够的工艺容差和鲁棒性。

- 新型结构:为了延续摩尔定律,鳍式场效应晶体管(FinFET)乃至环栅晶体管(GAAFET)等三维结构已取代传统平面MOSFET,以更好地控制沟道电流,减少漏电。

五、设计方法学:从器件到系统

现代IC设计是一个高度分层和自动化的过程:

- 电路级设计:基于SPICE仿真,对MOSFET电路进行直流、交流、瞬态和噪声分析,优化性能指标。

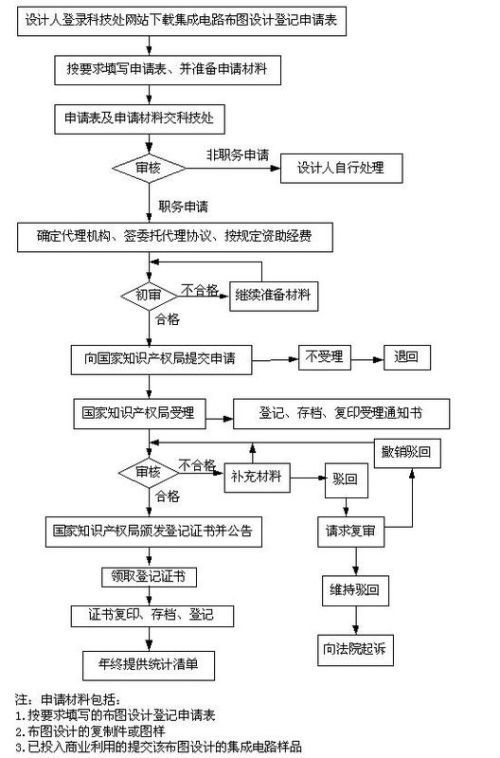

- 版图设计:将电路图转化为物理掩模图形。必须考虑器件匹配、寄生参数提取、天线效应、闩锁效应以及设计规则检查(DRC)和版图与电路图一致性检查(LVS)。

- 系统级考量:在更大的系统背景下,MOSFET电路的性能需与电源管理、时钟分布、信号完整性和热管理协同优化。

###

MOSFET电路知识是集成电路设计的通用语言和核心工具。从最基础的开关行为到应对最前沿的工艺挑战,深刻理解并娴熟运用MOSFET,是区分优秀工程师与普通工程师的关键。随着集成电路不断向更高性能、更低功耗、更多功能集成迈进,MOSFET及其衍生技术仍将是推动这场革命的永恒引擎。持续学习其深层次的物理机制和设计艺术,是每一位IC设计者职业生涯中不可或缺的旅程。